OP封装的存储器的脚端被出自处理芯片,电感耦合等离子体刻蚀机 公示TinyBGA是从处理芯片(中心)方向引出。这个方式有效地缩短了信号的传输距离,其同轴电缆长度只有传统OP工艺的1/4,信号衰减也有所减小。这样不但极大地提高了处理芯片的抗干扰和抗噪声性能,还提高了电气性能。 基材或中间层是BGA封装的重要组成部分,不仅可以用于连接布线,还可以用于电感/电阻/电容的阻抗控制和集成。

.jpg)

等离子体的直流电位以及离子轰击能量约为20~40V。与电容耦合等离子体相比较;电感耦合等离子体的离子通量和离子能 量可以得到更好的独立控制。为了更好控制离子轰击能量,电感耦合等离子体刻蚀机 公示一般会将另一个射频电源容性耦合在放衬底的晶圆上。线圈在感性放电的过程中会和容性驱动的衬底台产生容性耦合的成分,也就是在产生等离子体的过程中,外加电源会产生电压差。这将不利于等离子体密度和能量的独立控制。

这类电容ESL低,电感耦合等离子体刻蚀但ESR高,所以Q因数很低,频率范围很宽,非常适合板级电源滤波。品质因数越高,电感或电容两端的电压越高,附加电压也越高。在特定的频偏下,Q值越高,电流衰减越快,谐振曲线越尖锐。换言之,等离子表面处理器电路的选择性是由电路的Q因子决定的,功率一致性Q值越高,选择性就越高。等离子表面处理器电源完整性部分的解耦规划方法 为保证逻辑电路的正常工作,必须将电路逻辑状态的电平值降低一定的百分比。

从式中可以看出,电感耦合等离子体刻蚀过孔的直径对电感的影响较小,而对电感影响的是过孔的长度。

电感耦合等离子体刻蚀

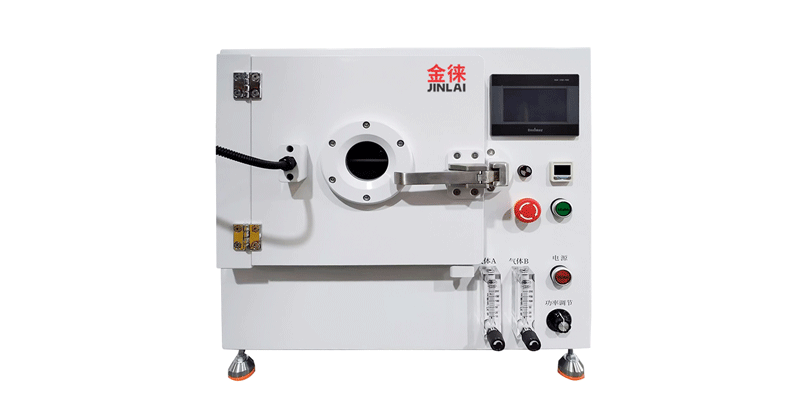

2、电感耦合等离子体机台:电感耦合等离子体机台是通过在反应腔室外的电磁线圈上加射频电压,在反应腔室中,急剧变化的感应磁场会在腔室中产生感应电场,使得初始电子获得能量继而产生低温等离子体的方法。电感耦合等离子体中电子会在围绕着磁力线回旋运动,较容性耦合机台中自由程更大,可以在更低的气压下激发出等离子体。等离子体密度可比电容耦合等离子体高约两个数量级,电离率可以达到1%~5%。

自旋转移矩磁存储器的制造也是通过在标准CMOS逻辑电路的后端金属连接层中心嵌入存储单元(磁性隧道结),并集成自旋转移矩逻辑后端电路来实现的。 .磁性隧道结和磁性隧道结的粗加工过程一目了然磁性隧道结蚀刻对于器件性能非常重要。目前使用的蚀刻技术包括等离子清洁器离子束蚀刻(ion beametching,IBE)、等离子清洁器电感耦合等离子蚀刻(ICP)、等离子清洁器反应离子蚀刻(RIE)等系统。

对比等离子蚀刻,湿法刻蚀是常用的化学清洗方法,其主要目的是使硅片表面的蒙版图形正确复制到涂胶硅片上,进而达到对硅片特殊区域的保护。自半导体制造业起步以来,硅片制造与湿法刻蚀系统就有着密切的联系。目前的湿法刻蚀系统主要用于除去残渣、漂浮去硅、大型图形刻蚀等,具有设备简单,选材比高,对器件损伤小等优点。

在plasma设备等离子氛围中,高分子材料表面链段上会形成自由基,这些自由基能够与离子源的自由基结合在高分子表面形成新的官能团。在等离子浸入干法刻蚀流程中,自由基的形成起着关键效用。比如,-般来讲高分子材料表面是疏水的,在引入一-些极性官能团后,材质表面会变的亲水,亲水的表面往往能大幅改善材质的黏附性能,提高其生物兼容性,将O2和水注入到这类的材质表面具有显著的(效)果。

电感耦合等离子体刻蚀

3、RIE外表刻蚀解决方案资料表面通过反应气体等离子被选择性地刻蚀,电感耦合等离子体刻蚀被刻蚀的资料转化为气相并被真空泵排出,处理后的资料微观比外表积增加并具杰出亲水性。 4、纳米涂层解决方案 通过等离子体的处理之后,等离子引导的聚合化作用构成纳米涂层。各类资料通过表面涂层,完成疏水性(疏水)、 亲水性(亲水)、疏脂性(防脂)、疏油性(防 油)。

蚀刻机原理电感耦合等离子体刻蚀(ICPE)是化学过程和物理过程共同作用的结果。其基本原理是在真空低气压下,电感耦合等离子体刻蚀机 公示ICP射频电源产生的射频以一定份额输出到环形耦合线圈;混合蚀刻气体通过耦合辉光放电产生高密度等离子体。在MI电极RF射频的作用下,这些等离子体外壳衬底表面,衬底图形区半导体数据的化学键断裂。挥发性物质随蚀刻气体产生,以气体形式离开基板并从真空管路抽走。蚀刻机与光刻机的区别蚀刻比光刻容易。

电感耦合等离子体刻蚀机,电感耦合等离子体刻蚀原理,电感耦合等离子体刻蚀 深圳,电感耦合等离子体刻蚀技术,电感耦合等离子体刻蚀系统,电感耦合等离子体刻蚀 铝,电感耦合等离子体刻蚀一般用什么气体